# OPERATING SYSTEM MANAGEMENT OF SHARED CACHES ON MULTICORE PROCESSORS

by

David Tam

A thesis submitted in conformity with the requirements for the degree of Doctor of Philosophy Graduate Department of Electrical and Computer Engineering University of Toronto

Copyright © 2010 by David Tam

#### **Abstract**

Operating System Management of Shared Caches on Multicore Processors

David Tam

Doctor of Philosophy

Graduate Department of Electrical and Computer Engineering

University of Toronto

2010

Our thesis is that operating systems should manage the on-chip shared caches of multicore processors for the purposes of achieving performance gains. Consequently, this dissertation demonstrates how the operating system can profitably manage these shared caches. Two shared-cache management principles are investigated: (1) promoting shared use of the shared cache, demonstrated by an automated online thread clustering technique, and (2) providing cache space isolation, demonstrated by a software-based cache partitioning technique. In support of providing isolation, cache provisioning is also investigated, demonstrated by an automated online technique called RapidMRC. We show how these software-based techniques are feasible on existing multicore systems with the help of their hardware performance monitoring units and their associated hardware performance counters. On a 2-chip IBM POWER5 multicore system, promoting sharing reduced processor pipeline stalls caused by cross-chip cache accesses by up to 70%, resulting in performance improvements of up to 7%. On a larger 8-chip IBM POWER5+ multicore system, the potential for up to 14% performance improvement was measured. Providing isolation improved performance by up to 50%, using an exhaustive offline search method to determine optimal partition size. On the other hand, up to 27% performance improvement was extracted from the corresponding workload using an automated online approximation technique, made possible by RapidMRC.

#### Acknowledgements

"If I have seen further, it is by standing on the shoulders of giants." - Isaac Newton

I am grateful to have been acquainted with some of my forefathers in the field of computer systems research, who have done pioneering work in operating system performance scalability: Orran Krieger, Ben Gamsa, Jonathan Appavoo, the University of Toronto Hurricane/Tornado/K42 OS group, and the IBM K42 OS group. It is their work that has led me to my research path.

This dissertation has been made possible by the generous support of many individuals. There are three individuals, in particular, whom I will forever be indebted. My supervisor, Professor Michael Stumm, has provided incomparable academic guidance and wisdom. My colleague, Reza Azimi, has made this dissertation possible; I cannot imagine how I could have done it without him. My colleague, Livio Soares, has been a vital source of inspiration with his positive outlook, boundless energy, humour, and chutzpah. I feel that the four of us together, as a paper publishing team, have conquered the world.

I would like to thank the other members of my research group, who have all enriched my Ph.D. graduate school experience, accompanying my years with intelligent and unique minds and personalities: Adam Czajkowski, Alex Depoutovitch, Raymond Fingas, Moshe Krieger, Maria Leitner, Adrian Tam, and Tom Walsh.

I am fortunate to have been aided by numerous individuals, external to my research group, during the production of this dissertation. I would like to thank: Allan Kielstra, Orran Krieger, Dilma Da Silva, Jimi Xenidis, and Santosh Rao, all five from IBM; Professor Cristiana Amza and Gokul Soundararajan, both at the University of Toronto; Professors Greg Steffan, Ashvin Goel, Angela Demke Brown, and Michael Voss, who are my departmental thesis committee members; and Professor Gernot Heiser, who is my external thesis committee member.

In terms of life support, I would like to thank my wife, Jennie Fan, for her patience and understanding. What seemed like eternity has finally passed. I am grateful to my parents for providing a supportive environment that has enabled me to reach this point in life's journey.

Finally, I would like to acknowledge my sources of financial support: the Edward S. Rogers Sr Department of Electrical and Computer Engineering at the University of Toronto, the Edward S. Rogers Sr National Electrical and Computer Engineering Scholarship Program, and the Government of Ontario through the Ontario Graduate Scholarship Program. This work was also supported by the Director, Office of Science, of the U.S. Department of Energy under Contract No. DE-AC02-05CH11231.

# Contents

| 1 | Inti | oduction and Motivation                                                    | 1    |

|---|------|----------------------------------------------------------------------------|------|

|   | 1.1  | Thesis and Goals of Dissertation                                           | . 4  |

|   | 1.2  | Dissertation Outline                                                       | . 4  |

|   |      | 1.2.1 Promoting Sharing                                                    | . 4  |

|   |      | 1.2.2 Providing Isolation                                                  | . 5  |

|   |      | 1.2.3 Provisioning the Shared Cache                                        | 6    |

|   | 1.3  | Collaboration with Colleagues                                              | . 8  |

|   | 1.4  | Research Contributions                                                     | . 9  |

| 2 | Bac  | kground                                                                    | 10   |

|   | 2.1  | Hardware Evolution                                                         | . 10 |

|   |      | 2.1.1 Moore's Law is Important                                             | . 11 |

|   |      | 2.1.2 Moore's Law is Impotent                                              | . 15 |

|   |      | 2.1.3 Moore's Law is Omnipotent: Rise of the (Multicore) Machines          | . 17 |

|   |      | 2.1.4 Multicore Processor Architecture Research                            | . 18 |

|   |      | 2.1.5 Multicore Processor Architectures Today                              | . 19 |

|   |      | 2.1.6 Key Hardware Characteristic of On-Chip Shared Caches                 | . 22 |

|   | 2.2  | Operating System Evolution                                                 | . 22 |

|   |      | 2.2.1 Single Processor Optimizations                                       | 23   |

|   |      | 2.2.2 Exploiting Multiple Processors                                       | . 25 |

|   |      | 2.2.3 Exploiting Simultaneous Multithreading                               | 31   |

|   |      | 2.2.4 Exploiting Multiple Cores                                            | . 32 |

|   |      | 2.2.5 Operating Systems: On the Move                                       | . 33 |

| 3 | Pro  | moting Sharing in the Shared Cache                                         | 37   |

|   | 3.1  | Introduction                                                               | . 38 |

|   | 3.2  | Related Work                                                               | 40   |

|   | 3.3  | Performance Monitoring Unit                                                | 43   |

|   | 3.4  | Design of Automated Thread Clustering Mechanism                            | 43   |

|   |      | 3.4.1 Monitoring Stall Breakdown                                           | 45   |

|   |      | 3.4.2 Detecting Sharing Patterns                                           | 45   |

|   |      | 3.4.3 Thread Clustering                                                    | 47   |

|   |      | 3.4.4 Thread Migration                                                     | 49   |

|   | 3.5  | Experimental Setup                                                         | 51   |

|   |      | 3.5.1 Platform-Specific Implementation: Capturing Remote Cache Accesses on |      |

|   |      | POWER5                                                                     | 51   |

|   |      | 3.5.2 Workloads                                                            | . 52 |

|   |      | 3.5.3 Thread Placement                                                     | 54   |

|   | 3.6  | Results                                                                    | . 54 |

|   |      | 3.6.1 Thread Clustering                                                    | 54   |

|   |     |          | Performance Results                                          |   |       |   |   |   |      |

|---|-----|----------|--------------------------------------------------------------|---|-------|---|---|---|------|

|   |     |          | Runtime Overhead and Temporal Sampling Sensitivity           |   |       |   |   |   |      |

|   |     |          | Spatial Sampling Sensitivity                                 |   |       |   |   |   |      |

|   | 3.7 |          | on                                                           |   |       |   |   |   |      |

|   |     |          | Local Cache Contention                                       |   |       |   |   |   |      |

|   |     |          | Migration Costs                                              |   |       |   |   |   |      |

|   |     | 3.7.3 I  | PMU Requirements                                             |   |       |   |   |   | . 6  |

|   |     | 3.7.4 I  | mportant Hardware Properties                                 |   |       |   |   |   | . 6  |

|   | 3.8 | Conclud  | ing Remarks                                                  |   |       |   |   |   | . 6  |

|   | ъ   |          |                                                              |   |       |   |   |   |      |

| 4 |     |          | solation in the Shared Cache                                 |   |       |   |   |   | 6    |

|   | 4.1 |          | etion                                                        |   |       |   |   |   |      |

|   | 4.2 |          | Work                                                         |   |       |   |   |   |      |

|   | 4.3 |          | of Cache Partitioning Mechanism                              |   |       |   |   |   |      |

|   |     |          | Space Partitioning the Cache                                 |   |       |   |   |   |      |

|   |     |          | Space Partitioning the Cache by Software                     |   |       |   |   |   |      |

|   | 4.4 | -        | entation of Cache Partitioning Mechanism                     |   |       |   |   |   |      |

|   |     |          | Page Allocation Within Cache Sections                        |   |       |   |   |   |      |

|   |     |          | Oynamic Partition Resizing                                   |   |       |   |   |   |      |

|   | 4.5 | Experim  | nental Setup                                                 |   |       |   |   |   | . 7  |

|   | 4.6 | Results  |                                                              |   |       |   |   |   | . 7  |

|   |     | 4.6.1 I  | mpact of Partitioning                                        |   |       |   |   |   | . 7  |

|   |     | 4.6.2    | Analysis of Interference                                     |   |       |   |   |   | . 7  |

|   |     | 4.6.3    | Stall Rate Curve Versus Miss Rate Curve                      |   |       |   |   |   | . 8  |

|   |     | 4.6.4 H  | Benefits of Dynamic Partition Resizing                       |   |       |   |   |   | . 8  |

|   |     | 4.6.5    | Costs of Dynamic Partition Resizing                          |   |       |   |   |   | . 8  |

|   | 4.7 | Discussi | on                                                           |   |       |   |   |   | . 8  |

|   | 4.8 | Conclud  | ing Remarks                                                  |   |       |   |   |   | . 8  |

|   |     |          |                                                              |   |       |   |   |   |      |

| 5 |     | •        | g the Shared Cache                                           |   |       |   |   |   | 8    |

|   | 5.1 |          | etion                                                        |   |       |   |   |   |      |

|   | 5.2 |          | und and Related Work                                         |   |       |   |   |   |      |

|   |     |          | Miss Rate Curves                                             |   |       |   |   |   |      |

|   |     | 5.2.2 I  | 22 MRC Generation                                            |   |       |   |   |   | . 9  |

|   |     | 5.2.3 I  | 2 Cache Partitioning and Provisioning                        |   |       |   |   |   | . 9  |

|   | 5.3 | Design a | and Implementation of RapidMRC                               |   |       |   |   |   | . 9  |

|   |     | 5.3.1    | Collecting Memory Access Traces                              |   |       |   |   |   | . 9  |

|   |     | 5.3.2 I  | 2 MRC Generation                                             |   |       |   |   |   | . 9  |

|   | 5.4 | Using R  | apidMRC to Provision the Shared Cache                        |   |       |   |   |   | . 10 |

|   | 5.5 | Experim  | nental Setup                                                 |   |       |   |   |   | . 10 |

|   | 5.6 | Results  |                                                              |   |       |   |   |   | . 10 |

|   |     | 5.6.1 N  | MRC Accuracy                                                 |   |       |   |   |   | . 10 |

|   |     | 5.6.2    | Overheads                                                    |   |       |   |   |   | . 11 |

|   |     | 5.6.3 I  | mpact of Trace Log Size                                      |   |       |   |   |   | . 11 |

|   |     |          | mpact of Warmup Period                                       |   |       |   |   |   |      |

|   |     |          | mpact of Missed Events                                       |   |       |   |   |   |      |

|   |     |          | mpact of Set Associativity                                   |   |       |   |   |   |      |

|   |     |          | mpact of Hardware Prefetching                                |   |       |   |   |   |      |

|   |     |          | mpact of Multiple Instruction Issue & Out-of-Order Execution |   |       |   |   |   |      |

|   | 5.7 |          | RC for Provisioning the Shared Cache                         |   |       |   |   |   |      |

|   | 5.8 | Discussi |                                                              | • | <br>• | • | • | • | 12   |

| 6 | Disc | cussion                                                                 | 127 |

|---|------|-------------------------------------------------------------------------|-----|

|   | 6.1  | Alternative Perspectives                                                | 127 |

|   | 6.2  | The Value of Hardware Performance Monitoring Units                      |     |

|   | 6.3  | Additional Hardware Extensions                                          |     |

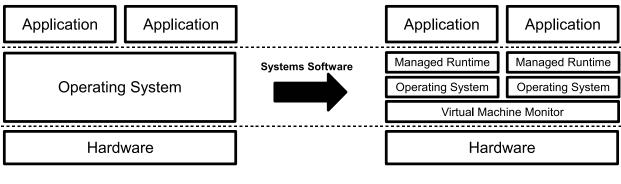

|   | 6.4  | Applicability to Other Layers of the System Stack                       | 129 |

|   |      | 6.4.1 Promoting Sharing in the Shared Cache                             | 130 |

|   |      | 6.4.2 Providing Isolation in the Shared Cache                           | 130 |

|   |      | 6.4.3 Provisioning the Shared Cache                                     | 131 |

|   | 6.5  | Limitations                                                             | 131 |

|   |      | 6.5.1 Cache Bandwidth Management                                        | 131 |

|   |      | 6.5.2 Hardware Performance Monitoring Unit Capabilities and Portability | 132 |

|   | 6.6  | Future Systems and Scalability                                          | 133 |

| 7 | Fut  | ure Work                                                                | 135 |

|   | 7.1  | Running More Workloads                                                  | 135 |

|   | 7.2  | Tuning and Improving Components                                         | 136 |

|   | 7.3  | Further Systems Integration                                             | 136 |

|   | 7.4  | Enabling Future Research                                                | 137 |

| 8 | Con  | nclusions                                                               | 139 |

|   |      |                                                                         |     |

# List of Tables

| 2.1 | Time line of commercially available general-purpose multicore processors 20 |

|-----|-----------------------------------------------------------------------------|

| 3.1 | IBM OpenPower 720 specifications                                            |

| 4.1 | IBM OpenPower 720 specifications                                            |

| 5.1 | Number of partition size combinations given a cache with 16 colors 95       |

| 5.2 | Number of partition size combinations given a cache with 64 colors 95       |

| 5.3 | IBM POWER5 specifications                                                   |

| 5.4 | LRU stack simulator specifications                                          |

|     | RapidMRC statistics                                                         |

# List of Figures

| 1.1  | Simplified views of a single-core and a multiple-core processor system          |       |

|------|---------------------------------------------------------------------------------|-------|

| 1.2  | Promoting sharing within a shared cache                                         |       |

| 1.3  | Providing isolation in a shared cache by partitioning it                        |       |

| 1.4  | A cache miss rate curve, used for cache provisioning                            | . 7   |

| 2.1  | Moore's Law on transistor growth and its impact on processor clock frequency    | . 11  |

| 2.2  | Parallelism by instruction pipelining                                           | . 12  |

| 2.3  | Extracting parallel instructions from a serial instruction stream               | . 14  |

| 2.4  | High-level internal organization of commercially available multicore processors | . 21  |

| 2.5  | A simplified view of an SMP multiprocessor                                      | . 26  |

| 2.6  | A simplified view of a NUMA multiprocessor                                      | . 30  |

| 2.7  | Traditional and new system stacks                                               | . 33  |

| 3.1  | IBM OpenPower 720 architecture                                                  | . 38  |

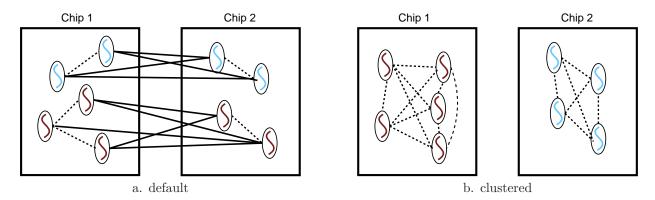

| 3.2  | Default versus clustered scheduling                                             | . 39  |

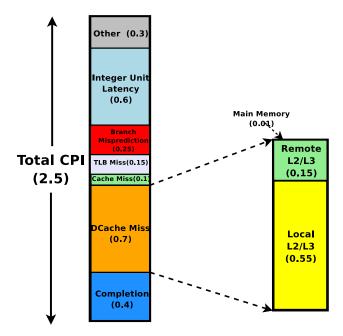

| 3.3  | Stall breakdown of VolanoMark                                                   | . 44  |

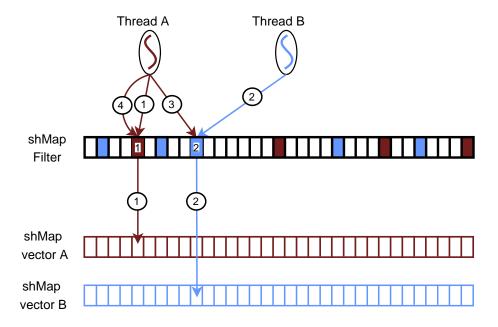

| 3.4  | Constructing shMap vectors                                                      |       |

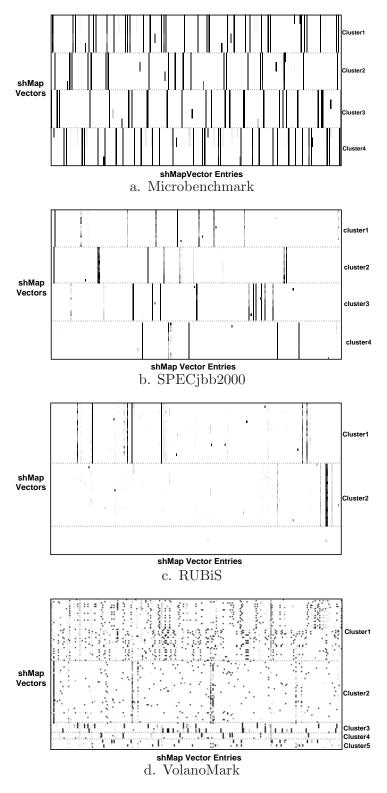

| 3.5  | A visual representation of clustered shMap vectors                              | . 56  |

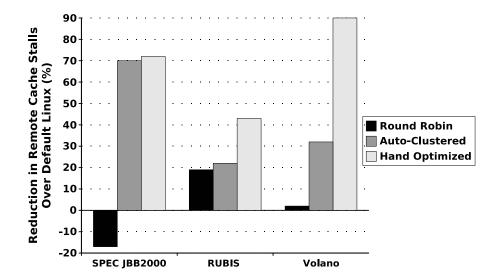

| 3.6  | Impact of thread clustering on reducing remote cache access stalls              |       |

| 3.7  | Impact of thread clustering on application performance                          |       |

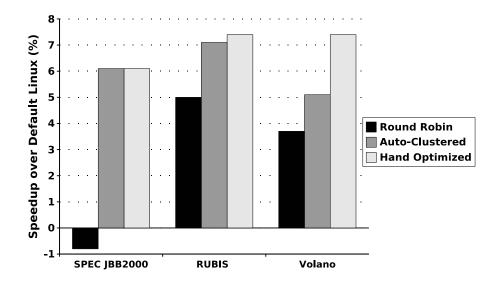

| 3.8  | Runtime overhead versus collection time trade-off spectrum                      |       |

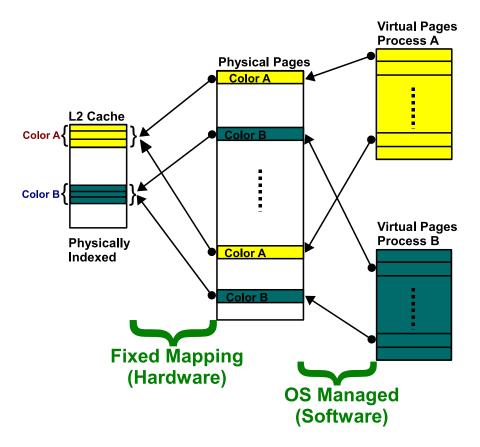

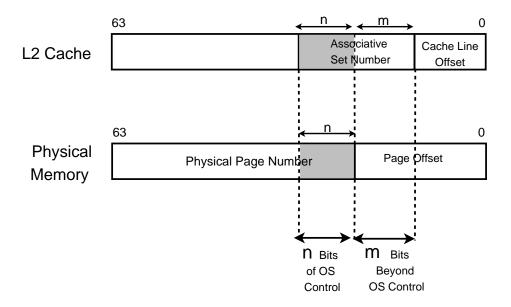

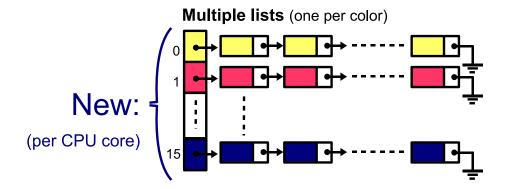

| 4.1  | Cache partitioning                                                              | . 66  |

| 4.2  | Page and cache section mapping                                                  |       |

| 4.3  | Bit-field perspective of mapping from physical page to cache section            |       |

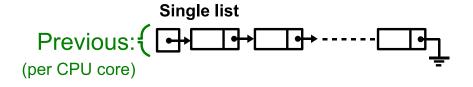

| 4.4  | Physical page free list modifications in Linux                                  |       |

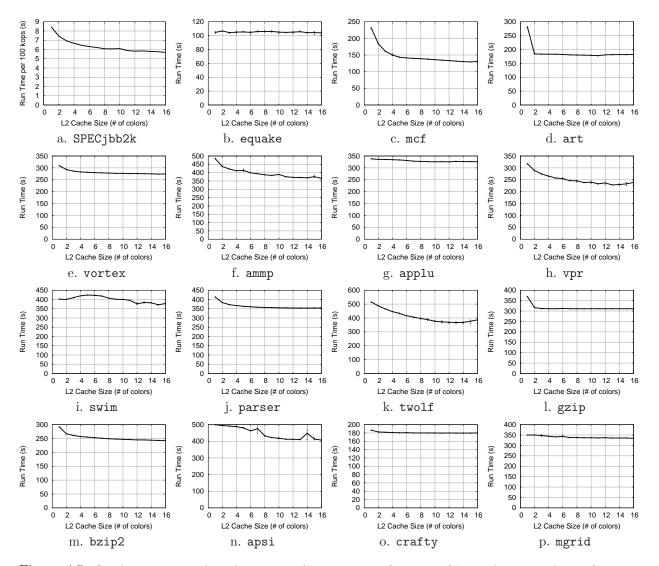

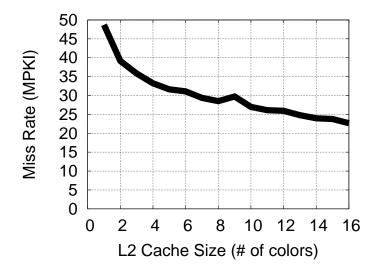

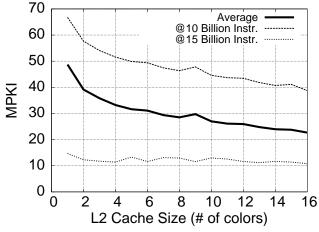

| 4.5  | Single-programmed application performance as a function of L2 cache size        |       |

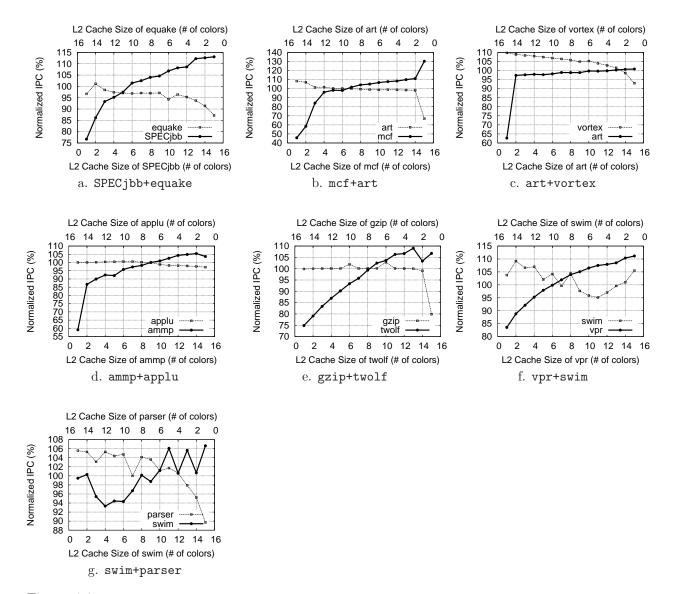

| 4.6  | Multiprogrammed workload performance as a function of L2 cache size             |       |

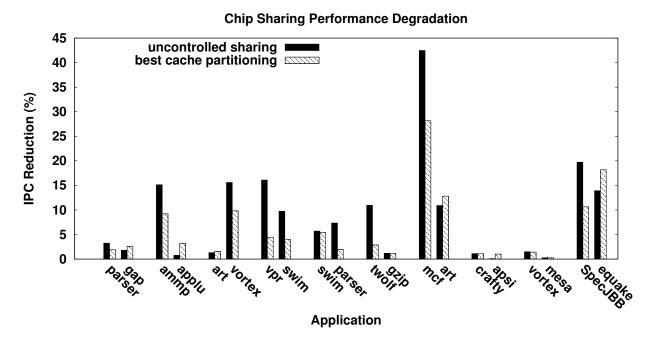

| 4.7  | Performance comparison with and without isolation                               |       |

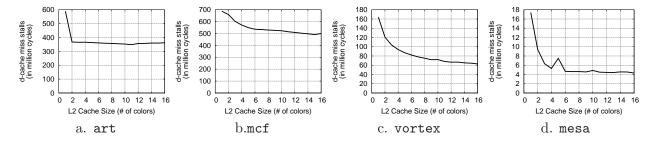

| 4.8  | Data cache stall rate curves                                                    | . 81  |

| 4.9  | L2 cache miss rate curves                                                       | . 81  |

| 4.10 | L3 victim cache and local memory hit rates for art                              |       |

| 4.11 | Effectiveness of dynamic partition resizing.                                    | . 83  |

|      | Overhead of dynamic partition resizing                                          |       |

| 5.1  | Offline L2 miss rate curve (MRC) of mcf                                         | . 90  |

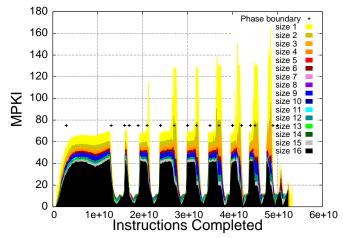

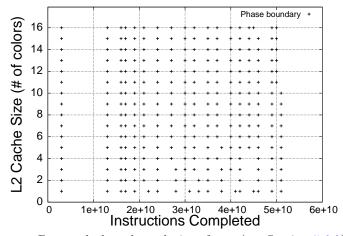

| 5.2  | Phase transitions in mcf and their impact on the L2 MRC                         | . 100 |

| 5.3  | Measured L2 cache miss rate as a function of time                               |       |

| 5.4  | Measured L2 cache miss rate as a function of time                               | . 102 |

| 5.5  | Measured L2 cache miss rate as a function of time                               | . 103 |

| 5.6  | Measured L2 cache miss rate as a function of time                               | . 104 |

| 5.7  | Measured L2 cache miss rate as a function of time                               |

|------|---------------------------------------------------------------------------------|

| 5.8  | Online RapidMRC vs offline real MRCs                                            |

| 5.9  | Improved RapidMRC for swim and art                                              |

| 5.10 | Impact of various factors on the calculated MRC of mcf                          |

| 5.11 | C language source code of the trace log microbenchmark                          |

| 5.12 | Histogram of missed events                                                      |

| 5.13 | A compact visualization of the microbenchmark trace log                         |

| 5.14 | Impact of prefetching on real & calculated MRCs                                 |

| 5.15 | Impact of multiple issue & out-of-order execution on real & calculated MRCs 121 |

| 5.16 | Chosen cache sizes and multiprogrammed workload performance                     |

### Chapter 1

### Introduction and Motivation

"Genius is one percent inspiration and ninety-nine percent perspiration." - Thomas Edison

A primary responsibility of operating systems is to manage the limited, shared, hardware resources of a computer and do so in a low-overhead manner. Traditionally, these resources included microprocessors (processors), main memory, disks, and network cards. Managing these resources intelligently in order to maximize performance or ensure fairness is a classic theme in operating systems research.

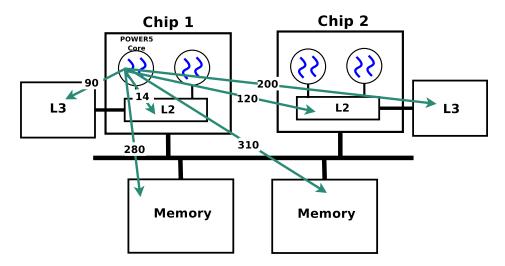

Due to the large speed disparity between processors and main memory, caches have been incorporated into processors. These on-chip caches are small but high-speed memories that serve as temporary buffers to larger but slower off-chip main memory. The on-chip caches are a performance-critical hardware resource because they can reduce data access latencies by an order of magnitude when compared to off-chip main memory access. For example, on the IBM POWER5 processor, accessing data that is located in the on-chip L2 cache requires 14 processor cycles, whereas accessing data that is located in main memory requires 280 cycles.

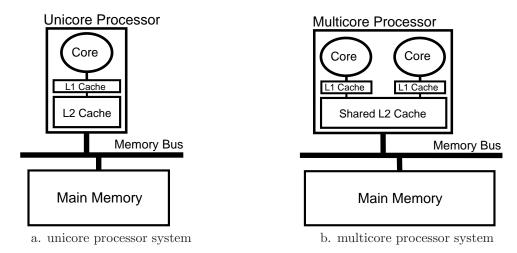

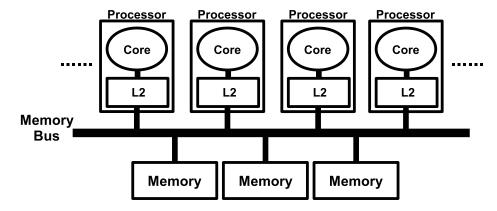

The recent arrival of multiple-core (multicore) processors has changed the hardware landscape considerably in that they have introduced on-chip caches that are *shared* by multiple execution cores. In contrast, previous generation single-core (unicore) processors featured an on-chip *private* cache that directly served only a single execution core. This introduction of sharing into such a performance-critical hardware resource can have a significant impact on performance. Figure 1.1a illustrates a simplified view of a traditional unicore processor, while Figure 1.1b illustrates a simplified view of a multicore processor.

In processors of today, there are typically 2 or 3 levels of on-chip cache. The level 1 (L1) cache is closest to the processor execution core and has the shortest access time but the lowest capacity. The level 2 (L2) cache is next in the cache hierarchy and has longer access times but larger capacity. Finally, there may be a level 3 (L3) cache with even longer access times but even larger capacity. On multicore processors, the last-level cache, which is the level before requiring off-chip main memory access, is typically shared among several cores. Typically, this component is the L2 cache or the

Figure 1.1: Simplified views of a traditional single-core (unicore) processor and a multiple-core (multicore) processor system.

#### L3 cache.

Although 2-core and 4-core processors are widely available today, the number of cores in future processors will only increase due to Moore's law, which predicts that the number of transistors on an integrated circuit will double approximately every 2 years [Moore 1965 1975]. For example, IBM recently began shipping the 8-core POWER7 processor; Sun currently offers the 8-core UltraSPARC T2 processor with future plans for a 16-core UltraSPARC T3 processor; AMD has a 6-core Opteron processor with plans for a 16-core processor; and Intel recently released an 8-core Xeon processor. Even game consoles use multicore processors. The Sony PLAYSTATION 3 uses the 9-core Sony-Toshiba-IBM Cell processor, while the Microsoft Xbox 360 features a 3-core Apple-IBM-Motorola PowerPC Xenon processor.

With the eminent ubiquity of multicore processors, we contend that their performance-critical on-chip shared caches are a hardware resource that should be intelligently managed by the operating system. On-chip caches have a limited size and therefore are a scarce, finite resource. Despite continual increases in the size of on-chip caches, the demand for cache space has always exceeded its supply because as on-chip cache sizes and the number of execution cores increase, so do application problem sizes. Future multicore processors will feature higher degrees of on-chip cache sharing, which may increase cache contention considerably and thus critically require operating system management. In this dissertation, we demonstrate how managing these shared caches at the operating system level can result in application performance improvements when compared to traditional operating systems that are not "shared cache"-aware. In managing shared caches at the operating system level, we address the challenges of maintaining low overhead and developing software-only techniques that are deployable on existing multicore processors of today.

We explore two management principles<sup>1</sup> to control how a shared cache is utilized by applications,

<sup>&</sup>lt;sup>1</sup>A definition of principle, according to the Oxford English Dictionary is, "II. Fundamental truth or law; motive force. 3. a. A fundamental truth or proposition on which others depend; a general statement or tenet forming the (or a) basis of a system of belief, etc.; a primary assumption forming the basis of a chain of reasoning."

which correspond to maximizing a major advantage and minimizing a major disadvantage of onchip shared caches. The first management principle promotes sharing of the cache by identifying

and facilitating shared usage among threads or processes. Once sharing is identified, threads or

processes can be scheduled in a manner that maximizes the occurrence of sharing within the on-chip

shared cached. For example, threads or processes that share data can be co-scheduled to all run

at the same time so that they can exploit the shared cache for sharing. As another example, on a

computer system consisting of multiple processor chips, where each chip is a multicore processor,

threads or processes that share data across processor chips can be migrated onto the same chip to

induce shared use of the local on-chip shared cache. Multiple threads of execution, which share a

single application address space, can intimately share a lot of data. In addition, multiple processes

with separate address spaces can often share common code libraries. They may also have regions of

their address space explicitly configured for shared access across processes. The first management

principle exploits a major advantage of a shared cache, namely its fast on-chip sharing capabilities.

Logical sharing at the software level, among threads or processes, can be mapped to a physically

shared resource at the hardware level, resulting in fast sharing.

The second management principle provides isolation in the shared cache by preventing non-sharing threads or processes from utilizing the same sections of the cache and interfering with each other's cache occupancy. In effect, a large shared cache can be partitioned into several smaller private caches. This principle circumvents a major disadvantage of shared caches, namely cache space interference among applications, where non-sharing threads or processes can inadvertently evict each other's data from the cache, leading to performance degradation.

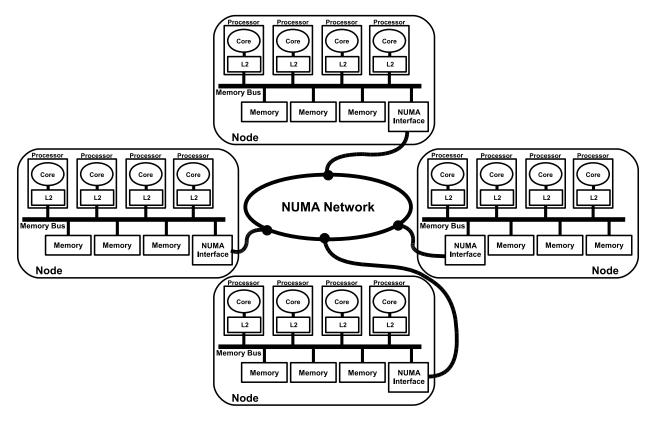

In traditional unicore processors and operating systems, these two management principles were not applicable to the on-chip caches since they were private rather than shared among multiple execution cores. However, these principles were applied in the past to main memory, since it can be viewed as a shared resource. For example, the first principle of promoting sharing can be seen in NUMA (non-uniform memory access latency) multiprocessor systems research. Traditionally, NUMA systems consist of multiple unicore processors that are grouped together in a hierarchical manner, with each group (node) containing local memory and the ability to access remote memory belonging to remote nodes. NUMA systems researchers have explored how to actively encourage sharing within the fast local memory of a node rather than allow sharing across slow remote memory of remote nodes [Appavoo et al. 2007; Bellosa and Steckermeier 1996; Gamsa et al. 1999]. Analogously in the realm of multicore systems, sharing at the software level among threads or processes can be mapped to an efficient shared resource at the hardware level, resulting in fast sharing capabilities.

The second principle of providing isolation can be seen in memory page or buffer management research that explores local policies as an alternative to global policies in an effort to reduce physical memory space interference between competing applications [Azimi et al. 2007; Choi et al. 2000; Soundararajan et al. 2008]. For example, in managing physical pages of a virtual memory system,

researchers have explored local per-region page replacement policies as an alternative to global page replacement policies [Azimi et al. 2007]. Analogously in the realm of multicore processors, preventing hardware resource interference among non-sharing, disparate threads or processes can result in performance improvements.

When providing cache space isolation to an application, cache space must be allocated to the application. Determining how much cache space to allocate to each application is another management role of the operating system. This task is typically known as *resource provisioning* and is required for scarce hardware resources, such as the on-chip shared cache. In this dissertation, we also explore how the operating system can determine the amount of on-chip cache space to allocate to each application.

#### 1.1 Thesis and Goals of Dissertation

Our thesis is that operating systems should manage the on-chip shared caches of multicore processors for the purposes of achieving performance gains. Consequently, the goal of this dissertation is to develop and demonstrate methodologies for how the operating system can profitably manage these shared caches. We develop and demonstrate methodologies to realize the two shared-cache management principles of *promoting sharing* and *providing isolation*. In support of providing isolation, we develop and demonstrate a methodology to provision the shared cache in an automated online manner.

#### 1.2 Dissertation Outline

To establish the context of our research, Chapter 2 provides general background on the evolution of computer hardware and operating systems. The principle of promoting sharing is investigated in Chapter 3, followed by the principle of providing isolation in Chapter 4. Provisioning the shared cache in support of providing isolation is investigated in Chapter 5. General issues that relate to all three components are discussed in Chapter 6. Future work is described in Chapter 7. Finally, we conclude in Chapter 8.

We now provide a brief overview of the two shared-cache management principles and shared cache provisioning.

#### 1.2.1 Promoting Sharing

The shared nature of on-chip caches is a property that can be exploited for performance gains. Data and instructions that are commonly accessed by all cores in a shared manner can be quickly reached by all cores. This hardware performance characteristic leads to our first principle of promoting sharing in the shared cache. An operating system scheduler could select processes or threads that

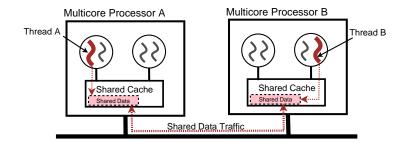

Figure 1.2: Promoting sharing within a shared cache. Thread A and thread B share data. Thread B could be migrated to multicore processor A so that the shared data is located within a single shared cache, resulting in faster access by both threads, leading to increased performance.

share data or instructions and co-schedule them to all run at the same time within the same multicore processor so that they can exploit the shared cache for sharing.

On a computer system consisting of multiple processor chips, each of which is a multicore processor, this goal involves migrating the sharing threads or processes, which may be scattered across several multicore chips, onto a single multicore chip. Figure 1.2 depicts a scenario where thread B could be migrated to multicore processor A so that the data shared between thread A and thread B can be located within a single shared cache. On a simpler computer system consisting of only a single multicore processor chip, thread or process migration is not applicable but simply co-scheduling the sharing threads or processes is sufficient to promote sharing. This scheme can also be applied to multiple processes, which don't share an address space but may share common code libraries. By promoting sharing, we exploit a major advantage of shared caches.

We develop and demonstrate a methodology that applies the principle of promoting sharing in Chapter 3. We target large multithreaded commercial workloads that execute in a single-programmed (single application) computing environment. On a small-scale multiple-chip platform<sup>2</sup>, we reduce processor pipeline stalls caused by cross-chip cache accesses by up to 70%, resulting in performance improvements of up to 7%. Preliminary results on a larger-scale multiple-chip platform<sup>3</sup> indicate the potential for up to 14% performance improvement.

In summary, we use operating system scheduling to promote sharing within the shared cache. By promoting sharing, we attempt to maximize a major benefit of shared caches, namely its fast sharing capabilities. We match the sharing that occurs in software with the available hardware sharing facilities.

#### 1.2.2 Providing Isolation

In some workload environments, sharing among processes or threads is not prevalent. An example would be a multiprogrammed, single-threaded computing environment, which consists of multiple applications that each have one thread of execution. In this situation, disparate processes, which

<sup>&</sup>lt;sup>2</sup>An 8-way IBM POWER5 system consisting of 2 chips  $\times$  2 cores per chip  $\times$  2 hardware threads per core.

$<sup>^3</sup>$ A 32-way IBM POWER5+ system consisting of 8 chips  $\times$  2 cores per chip  $\times$  2 hardware threads per core.

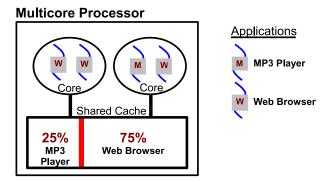

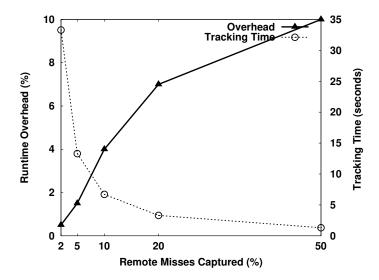

Figure 1.3: Providing isolation in a shared cache by partitioning it into smaller private caches. The MP3 player is allocated 25% of the L2 cache space for exclusive use, while the web browser is given the remaining 75%. This partitioning eliminates potential cache space interference between the two applications that would lead to performance degradation.

do not share any data or instructions, share the cache in an unrestricted manner and may interfere with each other when executing on the cores. Specifically, this situation can lead to cache line interference between non-sharing processes, resulting in significant performance degradation. A process may unintentionally evict cache lines belonging to a non-related process that is currently executing on another core of the processor rather than evict one of its own cache lines. Consider, for example, an MP3 player that streams through a lot of data without reuse. It severely and continuously pollutes the shared cache with an attendant negative effect on the performance of the other applications running on the other cores of the processor. This scenario of non-shared use of a shared hardware resource leads us to our second management principle of providing isolation in the shared cache. By providing cache space isolation, we circumvent a major disadvantage of shared caches.

We develop and demonstrate a methodology that applies the principle of providing isolation in Chapter 4. We control which processes or threads have access to which sections of the shared cache, as shown in Figure 1.3, and we can then effectively and flexibly partition the shared cache into smaller private caches. We accomplish this task at the operating system level by controlling the allocation of physical pages. We demonstrate performance improvements of up to 17% in terms of instructions-per-cycle (IPC).

In summary, we use operating system memory management to control the physical occupation of the shared cache in order to provide cache space isolation. By providing isolation, we attempt to minimize a major disadvantage of shared caches, namely cache space interference among applications.

#### 1.2.3 Provisioning the Shared Cache

A fundamental requirement of providing isolation is knowing how much cache space to allocate to each application. For example, when partitioning the shared cache in Figure 1.3, the operating system must decide upon an appropriate size for each partition. One possible solution is to use the

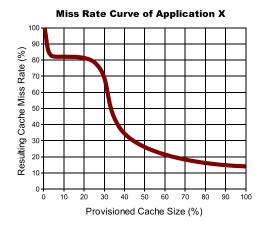

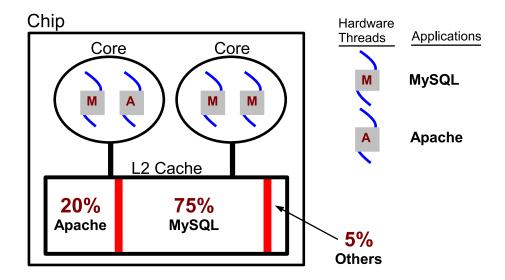

Figure 1.4: A cache miss rate curve showing the trade-off spectrum between provisioned cache size and the resulting cache miss rate. It characterizes the cache space requirements of the application and therefore can be used for cache provisioning.

trial-and-error technique of simply trying all possible partition sizes and monitoring the resulting application performance. Another solution is to take a more analytical approach by using the cache miss rate curve of the application to determine an appropriate size. Such a curve, as shown in Figure 1.4, reveals the trade-off spectrum between provisioned cache size and the resulting cache miss rate. It characterizes the cache space requirements of an application. Obtaining the miss rate curve of the on-chip cache in an online manner is a challenging problem on current processors, and it remains to be seen whether future processors will provide the necessary additional hardware support.

In Figure 1.4, the cache miss rate curve for an artificial application indicates that provisioning just 5% of the cache results in a miss rate of 80%, but that minor increases in the amount cache would have no impact until at least 25% of the cache is provisioned. Once past the 25% mark, there is a drastic benefit from increasing this amount until 45% of the cache is provisioned, at which point the cache miss rate drops from 80% to 30%. Provisioning any more than 45% of the cache has diminishing returns, decreasing the cache miss rate from 30% to 15%. Knowing this non-linear trade-off curve for each application provides powerful information for cache provisioning among multiple applications.

In Chapter 5, we develop and demonstrate a methodology to perform automated online cache provisioning. We demonstrate how the hardware performance monitoring unit (PMU) and its associated hardware performance counters found in current commodity processors can be used to obtain a low-overhead, online approximation of the miss rate curve of the on-chip shared cache. On average, it requires a single probing period of 147 ms and subsequently 83 ms to process the data. We show the accuracy of this approximation and its effectiveness when applied to the shared cache management principle of providing isolation so that an appropriate amount of cache space can be allocated to an application. Using this methodology, we demonstrate performance improvements of up to 27% in terms of instructions-per-cycle (IPC).

#### 1.3 Collaboration with Colleagues

Although the work in this thesis dissertation involved technical discussions and collaboration with colleagues, the core ideas, design, implementation, experimentation, and results were conceived, executed, and obtained by me.

In Chapter 3 on promoting sharing, I conceived the core idea of using PMUs to observe crosschip traffic and appropriately cluster threads. I designed and implemented the thread migration component and the workload configurations to exhibit the desired workload characteristics, as well as conducted the experiments. Expertise in hardware PMUs was provided by Reza Azimi, a fellow graduate student. We jointly designed the memory region tracking component and the thread clustering algorithm. The RUBiS database workload was generously provided by Professor Cristiana Amza and Gokul Soundararajan. This work resulted in a publication in the 2007 European Conference on Computer Systems (EuroSys), titled, "Thread Clustering: Sharing-Aware Scheduling on SMP-CMP-SMT Multiprocessors" [Tam et al. 2007b]. This publication forms the basis of Chapter 3, and has been cited by papers at major conferences, workshops, and magazines, such as ASPLOS [Eyerman and Eeckhout 2010; Gummaraju et al. 2008], SOSP [Baumann et al. 2009], OSDI [Boyd-Wickizer et al. 2008], HotOS [Boyd-Wickizer et al. 2009], PPoPP [Zhang et al. 2010], Communications of the ACM [Fedorova et al. 2010], and IEEE Micro Magazine [Knauerhase et al. 2008]<sup>4</sup>. Other citations include: [Bhadauria et al. 2008; Blagodurov et al. 2009; Blelloch et al. 2008; Durbhakula 2008; Hakeem et al. 2009; Jiang et al. 2010ab; Sáez et al. 2008; Schneider 2009; Shen and Jiang 2009; Sondag and Rajan 2009; Srikantaiah et al. 2009a; Sudheer et al. 2008; Vaddagiri et al. 2009; Xian et al. 2008].

In Chapter 4 on providing isolation, I conceived the idea of a software-based cache partitioning mechanism in my 2004 thesis proposal. I designed and implemented both the mechanism and the workload configurations, as well as conducted all experiments. Livio Soares, a fellow graduate student, provided additional performance analysis of the data in Section 4.6.2. This work resulted in a publication in the 2007 Workshop on the Interaction between Operating Systems and Computer Architecture (WIOSCA), titled, "Managing Shared L2 Caches on Multicore Systems in Software" [Tam et al. 2007a]. This publication forms the basis of Chapter 4, and has been cited by papers at major conferences, such as ASPLOS [Shen 2010; Srikantaiah et al. 2008], ISCA [Hardavellas et al. 2009], EuroSys [Zhang et al. 2009a], USENIX Annual Technical Conference [Zhang et al. 2009b], HPCA [Awasthi et al. 2009; Lin et al. 2008], PACT [Fedorova et al. 2007], and PPoPP [Hofmeyr et al. 2010]. Other citations include: [Chan 2009; Guan et al. 2009; Jin et al. 2009; Kotera 2009; Kumar and Delgrande 2009; Liu et al. 2009; Raj et al. 2009; Wu and Yeung 2009].

In Chapter 5 on provisioning the shared cache, I pursued the idea to track every L2 cache

$<sup>^4</sup>$ © ACM, 2007. Chapter 3 is a minor revision of the work published in Proceedings of the  $2^{nd}$  ACM SIGOPS/EuroSys European Conference on Computer Systems 2007 (March 21–23, 2007), http://doi.acm.org/10.1145/1272996.1273004

access using PMUs in order to generate approximated L2 cache miss rate curves (MRCs) online. I designed and implemented the RapidMRC system, as well as conducted the experiments. Reza provided the initial template code to configure the PMU. Well-known optimizations to Mattson's stack algorithm were implemented by Livio. This work resulted in a publication in the 2009 International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), titled, "RapidMRC: Approximating L2 Miss Rate Curves on Commodity Systems for Online Optimizations" [Tam et al. 2009]. This publication forms the basis of Chapter 5, and has been cited by papers at major conferences and magazines, such as ASPLOS [Zhuravlev et al. 2010], MICRO [Chaudhuri 2009], ISPASS [Xu et al. 2010], and Communications of the ACM [Fedorova et al. 2009 2010]<sup>5</sup>. Other citations include: [Blagodurov et al. 2009; Rai et al. 2009; Walsh 2009].

#### 1.4 Research Contributions

The contributions that stem from our research are demonstrated by the three publications generated from this thesis. To the best of our knowledge, we are the first, on commodity multicore systems, to develop and demonstrate a methodology for the operating system to:

- 1. promote sharing by clustering sharing threads based on runtime information obtained using hardware performance monitoring units (PMUs) [Tam et al. 2007b];

- 2. provide isolation by controlling occupation in the shared cache [Tam et al. 2007a];

- 3. provision the shared cache by approximating L2 cache miss rate curves online using hardware PMUs [Tam et al. 2009].

In each case, we developed a new mechanism and provided experimental evidence that it can be used to achieve performance gains. In two of our contributions, we also specifically contribute to the hardware PMU research community by concretely demonstrating profitable online usage cases of specific hardware PMU features [Azimi et al. 2009]. The three mechanisms developed as a part of our work create further research possibilities. Fellow researchers can use these initial mechanisms and ideas as a foundation or starting point for their own work, either further using, improving, and extending the base mechanisms, or to spawn or inspire related ideas. Chapter 7 describes some of the possible future work enabled by this dissertation. We hope we have opened up new research possibilities to the research community.

<sup>&</sup>lt;sup>5</sup>© ACM, 2009. Chapter 5 is a minor revision of the work published in Proceedings of the 14<sup>th</sup> International Conference on Architectural Support for Programming Languages and Operating Systems 2009 (March 7–11, 2009), http://doi.acm.org/10.1145/1508244.1508259

### Chapter 2

### Background

"Those who cannot learn from history are doomed to repeat it." - George Santayana

The purpose of this chapter is to provide a perspective on how this dissertation fits into the context of computer systems development, reviewing relevant advances in order to understand where we came from, how we arrived at the current state, and where we are potentially headed towards in the near and long term future. Subsequent chapters will each contain a section on prior work directly related to that chapter.

In this chapter, we first describe the evolution of hardware, followed by the evolution of operating systems. We describe the recurring pattern of how operating systems have been modified to first make functional usage of and then subsequently exploit new hardware features. We see how operating systems have actively managed shared, finite hardware resources to achieve performance improvements. Our research follows this well-accepted pattern of development and thus contributes to the evolution of computer systems.

#### 2.1 Hardware Evolution

In this section, we review the evolution of relevant hardware, beginning with the introduction of processors that fit onto a single integrated circuit, also known as microprocessors. From these processors, we describe how multiple-core processors came into existence, why they have become prevalent, and why we believe that they are here to stay. Understanding the evolution of hardware enables software researchers to investigate changes in the operating system to address current and anticipated future hardware.

We describe the development of various forms of parallelism to extract performance gains from applications, such as pipeline, instruction-level, multiprocessor, and thread-level. These previous developments ultimately led to the development of multiple-core processors.

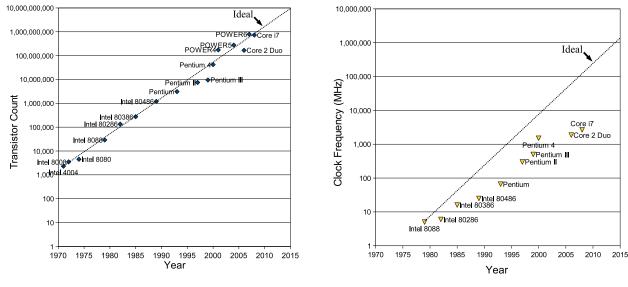

a. Moore's Law on transistor growth.

b. Impact on processor clock frequency.

Figure 2.1: Moore's Law on transistor growth and its impact on processor clock frequency [IBM 2007; Intel 2008a 2009 2005a; Sinharoy et al. 2005; Tendler et al. 2002]. Its impact on clock frequency has failed to keep up with the ideal trend, as shown for the Intel x86 family of processors.

#### 2.1.1 Moore's Law is Important

The first commercially available microprocessor on an integrated circuit was the Intel 4004, released in 1971 [Faggin et al. 1996]. In 1975, Gordon Moore famously predicted that the number of transistors on an integrated circuit would double every two years, revising his earlier prediction in 1965 that the number of transistors would double every year [Moore 1965 1975]. This prediction, known as Moore's Law, has been maintained, as shown in Figure 2.1a, because of advances in integrated circuit manufacturing that have continually shrunk the size of circuit elements.

At the transistor level, smaller circuit elements enable processors to operate at higher clock frequencies because the smaller transistors can be switched between the *on* and *off* states more quickly. In addition, signal propagation times are shorter because of shorter wires between these transistors.

The benefits from Moore's Law, faster transistors and an abundance of them enabling microarchitectural design improvements, have contributed to higher processor clock frequencies, as shown in Figure 2.1b for the Intel x86 processor family, although these increases have failed to keep up with the ideal trend. Thus, Moore's Law on transistor-count growth, although it does not make any prediction about processor clock frequency, has been very loosely correlated with such increases. Next, we review microarchitectural design improvements that have enabled further performance gains.

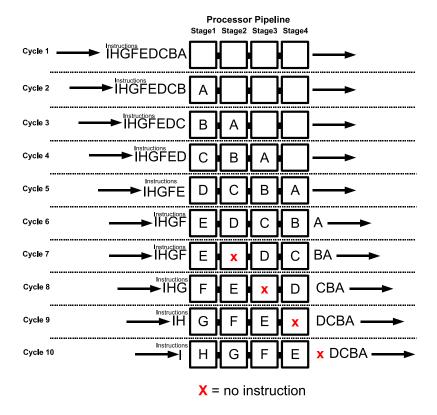

Figure 2.2: Parallelism by instruction pipelining. Although this technique enables higher processor clock frequencies, there may be cycles where no instructions are completed. Time progression is shown from top to bottom, while instructions flow through the processor pipeline from left to right. Each stage performs operations on a different instruction. A stall at clock cycle 7 in stage 2 eventually leads to no instruction completion at clock cycle 10.

#### Pipeline Parallelism

At the digital logic block level, another contributor to higher clock frequencies, given the abundance of transistors, is the use of the microprocessor architecture (microarchitecture) design technique of instruction pipelining. In pipelining, signal propagation through one large digital logic block is divided into several smaller digital logic block stages that have shorter signal propagation times, enabling shorter clock periods (higher clock frequencies). From a microarchitectural design perspective, instruction pipelining can be viewed as a form of parallelism because, at any point in time, when the pipeline is filled, each stage is performing an operation for a different instruction, such as shown in Figure 2.2 at clock cycle 6. In the figure, time progression is shown from top to bottom, while instructions flow through the processor pipeline from left to right. This instruction pipeline is analogous to the automobile assembly line where, at any point in time, each worker is operating in parallel to install a different component onto a different car, and by the end of the assembly line, the automobile is complete.

While the processor can operate at higher clock frequencies, the rate at which instructions are completed may not necessarily match. There may be clock cycles where no instructions are completed, as shown in Figure 2.2 at clock cycle 10, meaning that the average instructions-completed

per cycle (IPC) may fall below the ideal value of 1. This failure is due to stalls in the pipeline, which can come from a variety sources, including unavailable inputs to a pipeline stage, an operation within a stage taking several cycles to complete, or the inability of a pipeline stage to offload its outputs because of a full queue. For example, data may not be present because it is located off-chip in main memory, or floating-point operations may take several cycles to complete. In Figure 2.2, clock cycle 7 shows an example of where there was a stall in stage 2 of the pipeline that eventually leads to the lack of instruction completion at clock cycle 10.

In an attempt to reduce pipeline stalls and restore the IPC value to 1, various microarchitectural features were added to the pipeline, such as write forwarding, out-of-order execution, register renaming, and speculative execution based on branch prediction [Hennessy and Patterson 2007]. To deal with off-chip latencies leading to pipeline stalls, additional on-chip features have been included, such as on-chip floating-point units, various levels of caches, cache prefetching, and on-chip memory controllers. Moore's Law on transistor-count growth enabled all of these microarchitectural additions to fit within the processor chip.

#### Instruction-Level Parallelism

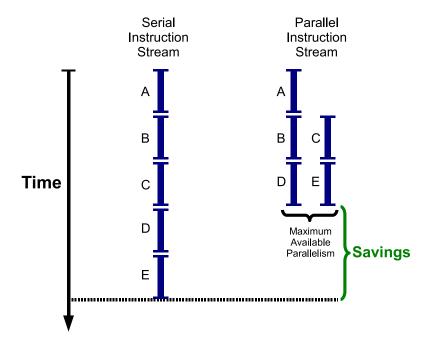

In an attempt to further raise the IPC value of the processor pipeline, microarchitecture researchers have added features to widen the pipeline, enabling potentially more than one instruction to complete within a single clock cycle, which is referred to as superscalar processing [Wall 1993]. Conceptually, these features attempt to extract parallelism from the application program, which is represented by a serial stream of instructions. They attempt to take the serial stream of instructions and extract instructions that can be executed in parallel with each other to shorten the total execution time, as shown in Figure 2.3. It is important to note that only instructions that do not directly or indirectly depend upon each other for input or output values can be executed in parallel. Given this constraint, the number of instructions that can be executed in parallel is known as the available instruction-level parallelism (ILP) of the serial instruction stream. For example, in Figure 2.3, instructions B and C depend only upon the result of instruction A. Instruction D depends only upon the result of instruction B. Instruction E depends only upon the result of instruction C. The resulting ILP of the instruction stream is 2 at its maximum and  $1.\overline{6}$  on average. To exploit the available ILP, some features were introduced to widen the pipeline, including: multiple instruction issue and execution, multiple functional units, and vector units [Hennessy and Patterson 2007]. Again, Moore's Law on transistor-count growth enabled these microarchitectural additions to fit within the processor chip.

These hardware improvements, combined with compiler optimizations to exploit these facilities, were conceived with the goal of requiring no application-level modifications. Thus, software applications have had the luxury of experiencing performance gains without requiring application redesign or re-implementation.

Figure 2.3: To increase the number of instructions completed per processor clock cycle, parallel instructions can be extracted from a serial instruction stream as long as they adhere to data dependencies between instructions. If instructions B and C depend only upon the result of instruction A, instruction D depends only upon the result of instruction B, and instruction E depends only upon the result of instruction C, then the maximum available instruction-level parallelism for this instruction stream is 2.

#### Multiprocessor Parallelism

Despite these performance improvements to single processors, one can always find larger and more sophisticated problems that need to be solved more quickly. A single processor still cannot meet the performance requirements of numerous important applications. This deficit led to the application of multiple microprocessors, within one computer and across multiple computers, leading to increased computer systems research in the area known as parallel and distributed systems. Examples of these multiple processor systems include SMP (symmetric multiprocessing) multiprocessors; NUMA (non-uniform memory access latency) multiprocessors; and clusters consisting of multiple computers (workstations, servers, blades), each one potentially being a multiprocessor itself.

Unfortunately, these multiple processor systems have largely remained in a specialized, niche computing domain which has had little applicability to the majority of the general computer world. It remains debatable as to the reason for the unpopularity of these traditional multiple processor systems. There appears to be many factors, such as (1) the difficulty in developing parallel versions of applications since software modifications are required, unlike the previous hardware improvements, (2) the once seemingly never-ending exponential single processor performance improvements incidentally linked to Moore's Law on transistor counts, and (3) the nonlinear hardware costs associated with increasing multiprocessor system size. Perhaps it is the combined effect of these factors that have allowed application developers to make more productive use of their time by simply waiting a few months for faster processors to become available for the same price as the previously acquired

ones, enabling single-processor applications to execute faster without additional programmer effort. However, this phenomenon has largely come to an end because processor manufacturers are now unable to viably develop processors with higher clock frequencies.

#### 2.1.2 Moore's Law is Impotent

The end to single processor speed increases has little to do with Moore's Law. Moore's Law makes no claim with respect to processor speeds, but only on the number of transistors on a chip. Due to various electrical engineering factors, such as power dissipation and the constant speed of light affecting signal propagation delays, the frequency at which these transistors can be switched on and off is reaching its limit, which leads to a limit on the processor clock frequency. In addition, there are microarchitectural limitations, such as the complexity of extracting additional pipeline parallelism and instruction-level parallelism (ILP) from the serial instruction execution stream, the increasing complexity of monolithic processor designs, and relatively longer on-chip wire delays in traversing the chip [Wall 1993]. Straight-forward extensions to existing monolithic microarchitectural innovations, outlined in the previous subsections, appear to be inadequate for extracting further performance improvements from the executing software instructions.

From a mathematical perspective, performance within a processor family, such as the Intel x86 family, can be measured by the number of instructions completed per second (IPS: instructions per second), and is a result of the following.

$$IPS \frac{\text{instructions}}{\text{second}} = IPC \frac{\text{instructions}}{\text{cycle}} \times clock\_frequency \frac{\text{cycles}}{\text{second}}$$

(2.1)

To increase the value of IPS, and thus performance,  $clock\_frequency$  could be increased, or IPC could be increased. Unfortunately,  $clock\_frequency$  now appears capped and IPC has limited potential due to difficulty in extracting instruction-level-parallelism (ILP) from a single serial instruction stream. Moore's Law no longer correlates to higher  $clock\_frequency$  values. However, Moore's Law does provide extra transistors that can help increase IPC in other ways.

#### Thread-Level Parallelism

From an architectural perspective, now that the easily-available instruction-level parallelism (ILP) has been harvested, the next unexploited source for IPC improvements lies in the availability of thread-level parallelism (TLP). TLP describes the scenario where there are multiple, independent threads of execution, which can be run simultaneously within a single processor. These multiple threads can come from either within a single application or across multiple applications. This scenario is similar to the traditional multiprocessor parallelism scenario described in a previous section, where multiple threads are executed on multiple processors. By exploiting thread-level parallelism, microarchitecture researchers have taken a page out of the book of computer systems researchers, inheriting some of the advantages and disadvantages in exploiting multiprocessor par-

allelism. Thread-level parallelism enables the IPC term in Equation 2.1 to become the sum of the IPC of each thread, as shown in Equation 2.2 for N threads.

$$IPS = \left(\sum_{n=1}^{N} IPC_n\right) \times clock\_frequency$$

, given N threads (2.2)

The potential of thread-level parallelism within a single processor led to research in, and development of, various initial forms of hardware multithreading, and eventually led to the development and commercial availability of simultaneous multithreading (SMT) processors [Lo et al. 1997; Marr et al. 2002; Tullsen et al. 1995]. Similar to how a software-based multithreading mechanism maintains the context of multiple threads in main memory, SMT processors maintain the context of multiple threads but in designated hardware structures. With such hardware support, these threads are also known as hardware threads. This hardware extension enables the microarchitectural components to simultaneously process instructions from multiple hardware threads, rather than from just a single thread, thus extracting the parallelism found across multiple threads. In fact, hardware multithreading leverages much of the existing microarchitecture infrastructure that was previously designed to extract instruction-level parallelism (ILP) from a single thread, by feeding multiple independent streams of instructions into the processor pipeline Burns and Gaudiot 2002. SMT processors offer approximately a 25% performance increase on average, while costing only 5% more in transistor count, with a relatively straight-forward retrofit to existing out-of-order pipelined, superscalar microarchitectures [Koufaty and Marr 2003]. From a software point of view, for both the operating system and applications, SMT processors appear like multiple processors, with each hardware thread appearing as a separate traditional processor. This view enabled existing multiprocessor operating systems to run on SMT processors with few modifications, if any.

#### Memory Wall

Another issue limiting performance is the large and growing disparity between raw processor speeds and off-chip main memory speeds in terms of both latency and bandwidth. This disparity is commonly referred to as the *memory wall*. Access latencies to off-chip versus on-chip memory is typically an order of magnitude larger. For example, in the IBM POWER5 processor, accessing the on-chip L2 cache requires 14 processor cycles, whereas accessing the off-chip local main memory requires 280 cycles. In particular, the problem of limited off-chip memory bandwidth on processors has been noted by numerous researchers [Burger et al. 1996; Huh et al. 2001; Rogers et al. 2009]. While the number of transistors on a chip has increased at a rapid rate, the number of external pins and their associated speeds have not increased proportionately. Future processors will encounter the fundamental problem of shipping data into and out of the chip quickly enough, in terms of latency and bandwidth, to meet the demands of the ever-growing number of processing elements, caused by Moore's Law on transistor-count growth.

#### 2.1.3 Moore's Law is Omnipotent: Rise of the (Multicore) Machines

The potential of thread-level parallelism (TLP), in combination with the unrelenting pace of Moore's Law, the uncoupling of processor speed from transistor count, and the rising memory wall, subsequently led to the development and commercial availability of multiple-core (multicore) processors. From a mathematical perspective, Equation 2.2 again meant that multiple threads, from TLP, was the only source of performance increase. In fact, the only feasible avenue for future performance increases appears, at this time, to be from increasing the number of hardware threads and from increasing the number of cores, given that the IPC of an individual thread appears to have reached its limit.

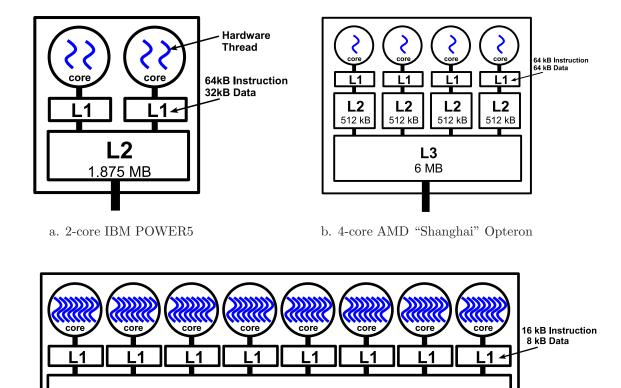

Multicore processors consist of several execution cores located on a single chip, in contrast to traditional single-core processors, which contain only a single execution core. SMT processors, in comparison, consist of a single core in which many microarchitectural resources within the core are shared by multiple hardware threads, whereas in multicore processors, microarchitectural resources within a core are private and only the on-chip L2 or L3 cache is potentially shared among the cores. SMT and multicore technologies are complementary and can be combined to create multicore-SMT processors, such as the IBM POWER5 or Intel Core 2 processors, both consisting of 2 cores in which each core contains 2 SMT threads. An illustration of the IBM POWER5 multicore-SMT processor is show in Figure 2.4a.

With transistor counts doubling periodically, chip designers could simply stamp out twice the number of cores on a chip and easily double the *raw* processing capabilities, assuming that there are enough threads to utilize all available cores. In effect, it can be seen as a divide and conquer approach. Now, the only problem left in this distributed environment on the chip, from a hardware point of view, is communication. Microarchitectural research can place more effort in on-chip interconnection networks, and on-chip cache organizations. Hierarchical, non-uniform designs appear to be the future of multicore processors and are now an active research area for the computer architecture community [Beckmann and Wood 2004; Dybdahl et al. 2007; Huh et al. 2005; Zhang and Asanović 2005].

Multiple-core processors were initially given the term, "single-chip multiprocessors", or more simply "chip multiprocessors" (CMP), because they appeared similar to a traditional SMP multiprocessor but with all of its processors located on a single chip. Eventually, once Intel finally began selling these kinds of processors, a simpler name evolved and they are now popularly known as "multicore" processors.

While the challenge of effectively utilizing the abundance of transistors, from a hardware perspective, has been addressed by the rise of multicore processors, the challenge of the memory wall still persists. Architecture and compiler researchers have explored solutions such as hardware-based [Chen and Baer 1995], compiler-extracted [Luk and Mowry 1999], and programmer-directed [Cher et al. 2004] prefetching. This line of research concentrates on the problems of predict-

ing what to prefetch, when to prefetch it so that it is available in a timely manner given the large memory wall, how to balance prefetcher memory requests against program-requested (demand-based) memory requests, and how to prevent prefetched data from polluting the demand-based data in the on-chip caches. The scope of prefetching research is limited to predicting what data will be required in the future and making it available in a timely manner. It does not deal with the management of demand-based data, such as promoting shared use of demand-based data among multiple threads, and preventing interference among demand-based data among multiple applications. Prefetcher research is complementary to operating system runtime management of on-chip shared caches.

As in the past, people will always find larger problems to solve that will exceed the performance capacity of a single processor system, even if it is a multicore processor. Thus, similar to the past, computer systems consisting of several chips, this time, each being a multicore processor, will serve an important role in fulfilling these higher-end computing needs. Major computer systems vendors, such as IBM, HP, Dell, and Sun, currently sell these multichip systems, which are more commonly referred to as *multisocket* systems because each chip sits in its own socket on the system board. Multisocket system boards for AMD and Intel multicore processors are also commercially available for user-assembled systems. As in the past, in order to fully utilize the full performance potential of this hardware, the operating system must be aware of these new hardware characteristics and optimize for them.

#### 2.1.4 Multicore Processor Architecture Research

Architecture researchers at Stanford University were among the first to advocate general-purpose multicore processors [Olukotun et al. 1996]. Sohi went further and advocated radical re-architecting of multicore chips [Sohi 2003]. There have been several research multicore processors, such as Hydra [Hammond et al. 2000], Piranha [Barroso et al. 2000], and Atlas [Codrescu et al. 2001]. These projects explored issues such as microarchitectural design, compiler support, and speculative execution of user-level applications. Operating system design has not been a major focus of these projects.

Hardware-oriented research in on-chip cache organizations of multicore processors has been an active area because these caches are critical to overcoming the memory wall between processor and main memory speeds. Architecture researchers have proposed variations to: (1) the cache coherence protocols of various cache organizations [Chang and Sohi 2007 2006; Chishti et al. 2005; Liu et al. 2004]; (2) the cache line insertion [Jaleel et al. 2008] policy; (3) the cache line replacement policy [Dybdahl et al. 2006; Qureshi and Patt 2006; Srikantaiah et al. 2008; Suh et al. 2004]; (4) the sizes of caches and interconnects [Hsu et al. 2005; Zhao et al. 2007b]; (5) the organization of the caches and interconnects, such as tiled, and non-uniform hierarchies [Dybdahl et al. 2007; Huh et al. 2005; Kumar et al. 2005]; and (6) policies affecting performance, fairness, or quality of service [Hsu et al. 2005 2006; Iyer 2004; Iyer et al. 2007; Kannan et al. 2006; Zhou et al. 2009]. Again, operating

system design or co-design has not been a major focus of these projects.

The focus of this dissertation is not on microarchitectural improvements, but on how to exploit the given new hardware characteristics of multicore processors from an operating system's point of view, extracting as much performance as possible. While architecture researchers play an important role in finding good and efficient uses of more and more transistors, operating systems researchers have the potentially multiple research roles of (1) exploiting the given hardware architectures to extract the most performance for the software levels above, and (2) making suggestions to architecture researchers on how the interaction between the architecture and operating system can be improved to extract more performance from hardware. In this dissertation, we concentrate on the first role, but also provide a few suggestions on additional hardware support.

#### 2.1.5 Multicore Processor Architectures Today

Multicore processors have existed in the realm of embedded devices since at least 1994. Some examples of such embedded multicore processors include: (1) the Texas Instruments TMS320C80 multimedia video processor in 1994, consisting of 1 general-purpose core and 4 digital signal processing cores [Texas Instruments 1994]; (2) the Motorola MPC821 PowerQUICC communications processor in 1995, consisting of 1 general-purpose core and 1 special-purpose communications core [Motorola 1998]; (3) the Broadcom BCM1250 network processor in 2001, consisting of 2 general-purpose cores [Broadcom 2001]; and (4) the Sun MAJC 5200 media processor, announced in 1999 and finally shipped in 2002, consisting of 2 general-purpose cores [Sun 1999 2002].

In the realm of general-purpose computing (i.e., laptop, desktop, and server computers), general-purpose multicore processors have been commercially available since 2001 with the release of the IBM POWER4 multicore processor. Table 2.1 shows a time line of commercially available multicore processors for general-purpose computers. It indicates wide gaps in time between the introduction of the first general-purpose multicore processor by IBM in 2001, the subsequent releases by other general-purpose processor manufacturers in 2004, and the eventual mainstream acceptance of general-purpose multicore processors in 2005, signalled by the release of multicore processors by Intel and AMD. Our work in this dissertation is applicable to both embedded and general-purpose multicore processors that contain on-chip shared caches.

A common design theme is the use of on-chip shared caches, typically at the final cache level before requiring access to off-chip caches or main memory, commonly known as the *last-level* cache. For most processors, this last-level cache is the L2 cache, and for a few others, this last-level cache is the L3 cache. These two characteristics are specified in the columns labelled "Shared Caches" and "On-Chip Caches" in Table 2.1, respectively.

As concrete examples of the high-level organization of the multiple cores and caches within these commercially available processors, Figure 2.4 shows simplified diagrams of a 2-core IBM POWER5, a 4-core AMD "Shanghai" Opteron, and an 8-core Sun "Niagara 2" UltraSPARC T2 processor. The POWER5 contains a 1.875 MB L2 cache that is shared among 4 SMT hardware threads from

| Ship  |                                    | On-Chip        | Shared |                         |  |  |  |  |

|-------|------------------------------------|----------------|--------|-------------------------|--|--|--|--|

| Date  | Multicore Processor                | Caches         | Caches | Citations               |  |  |  |  |

|       |                                    | 001            |        |                         |  |  |  |  |

| Oct.  | 2-core IBM POWER4                  | L1,L2          | L2     | [IBM 2001]              |  |  |  |  |

|       | 20                                 | 002            |        |                         |  |  |  |  |

|       |                                    | 003            |        |                         |  |  |  |  |

|       | 20                                 | 004            |        |                         |  |  |  |  |

| Feb.  | 2-core HP PA-8800                  | L1             | none   | [HP 2004]               |  |  |  |  |

| Mar.  | 2-core Sun UltraSPARC IV           | L1             | none   | [Sun 2004ab]            |  |  |  |  |

| May   | 2-core IBM POWER5                  | $_{\rm L1,L2}$ | L2     | [IBM 2004]              |  |  |  |  |

|       | 20                                 | 005            |        |                         |  |  |  |  |

| Apr.  | 2-core Intel Pentium               | L1,L2          | none   | [Intel 2005b]           |  |  |  |  |

| Apr.  | 2-core AMD Opteron                 | L1,L2          | none   | [AMD 2005]              |  |  |  |  |

| Oct.  | 2-core IBM PowerPC970MP            | $_{\rm L1,L2}$ | none   | [Apple 2005; IBM 2005b] |  |  |  |  |

| Nov.  | 3-core IBM-Microsoft PowerPC Xenon | $_{\rm L1,L2}$ | L2     | [Microsoft 2005]        |  |  |  |  |

| Dec.  | 8-core Sun UltraSPARC T1           | $_{ m L1,L2}$  | L2     | [Sun 2005]              |  |  |  |  |

|       | 20                                 | 006            |        |                         |  |  |  |  |

| Jul.  | 2-core Intel Itanium 2             | L1,L2,L3       | none   | [Intel 2006b]           |  |  |  |  |

| Sept. | 9-core Sony-Toshiba-IBM Cell       | $_{ m L1,L2}$  | none   | [IBM 2006; Sony 2006]   |  |  |  |  |

| Nov.  | 4-core Intel Xeon & Core 2 Extreme | $_{ m L1,L2}$  | L2     | [Intel 2006a]           |  |  |  |  |

|       |                                    | 007            |        |                         |  |  |  |  |

| Apr.  | 2-core Sun-Fujitsu SPARC64 VI      | L1,L2          | L2     | [Fujitsu 2007]          |  |  |  |  |

| May   | 2-core IBM POWER6                  | $_{\rm L1,L2}$ | none   | [IBM 2007]              |  |  |  |  |

| Sept. | 4-core AMD Opteron                 | L1,L2,L3       | L3     | [AMD 2007]              |  |  |  |  |

| Oct.  | 8-core Sun UltraSPARC T2           | $_{ m L1,L2}$  | L2     | [Sun 2007]              |  |  |  |  |

|       |                                    | 008            |        |                         |  |  |  |  |

| Sept. | 6-core Intel Xeon                  | L1,L2,L3       | L3     | [Intel 2008b]           |  |  |  |  |

| Oct.  | 4-core Sun-Fujitsu SPARC64 VII     | $_{\rm L1,L2}$ | L2     | [Fujitsu 2008]          |  |  |  |  |

| 2009  |                                    |                |        |                         |  |  |  |  |

| Jun.  | 6-core AMD Opteron                 | L1,L2,L3       | L3     | [AMD 2009]              |  |  |  |  |

|       | 2010                               |                |        |                         |  |  |  |  |

| Feb.  | 4-core Intel Itanium 2             | L1,L2,L3       | none   | [Intel 2010a]           |  |  |  |  |

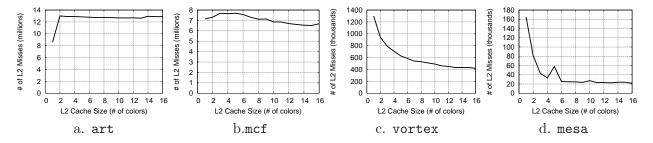

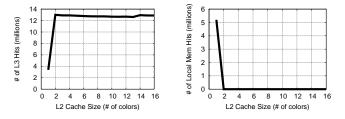

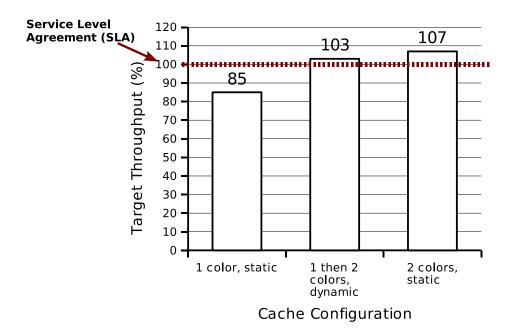

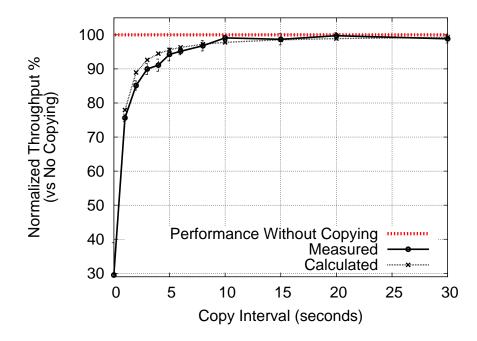

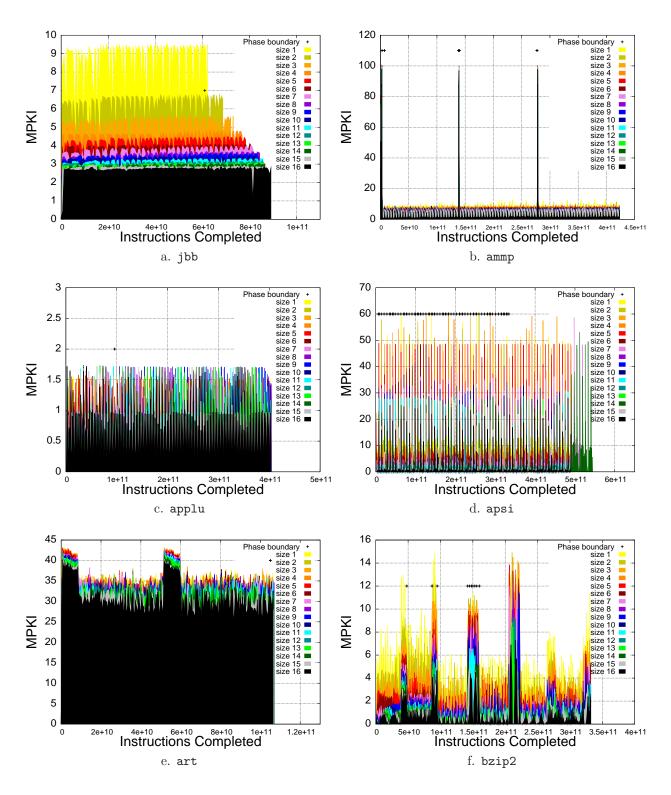

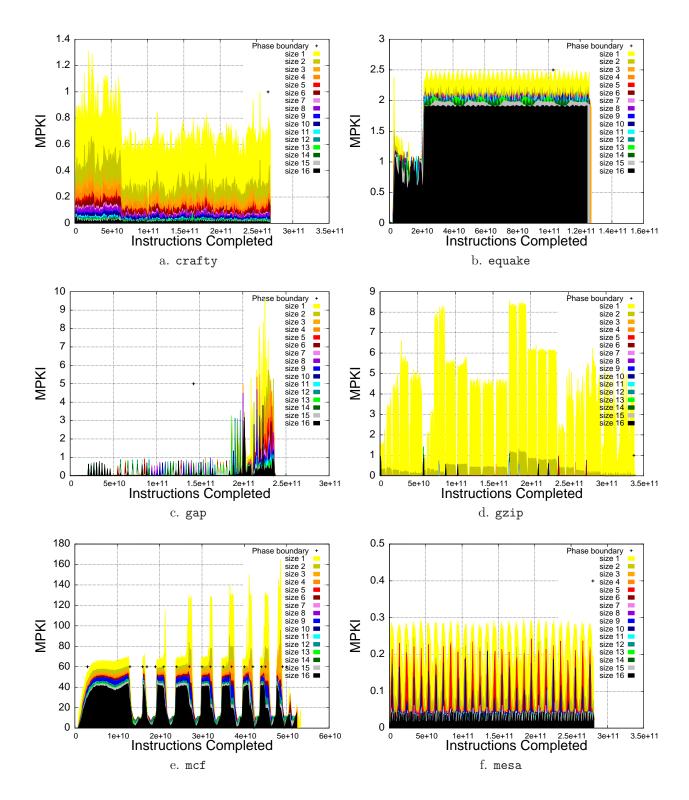

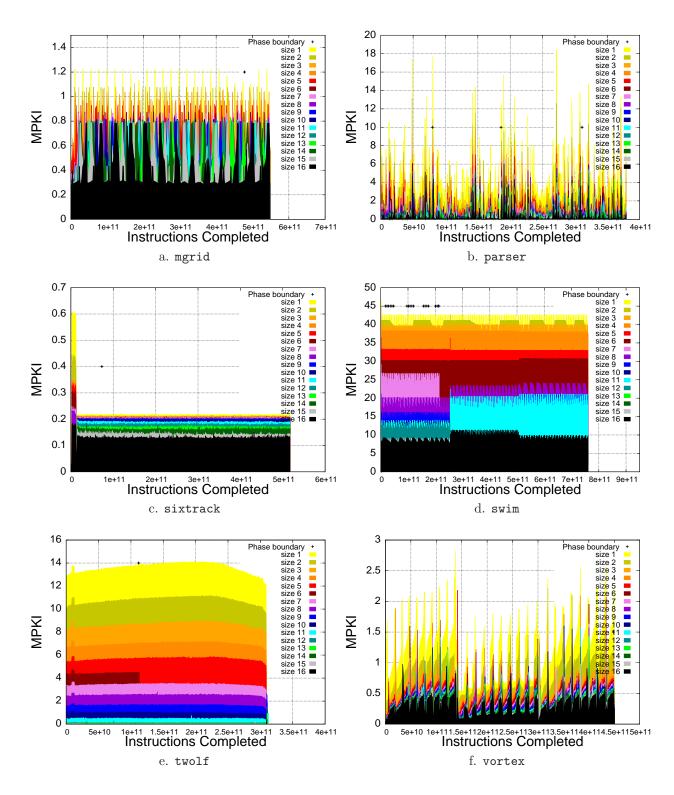

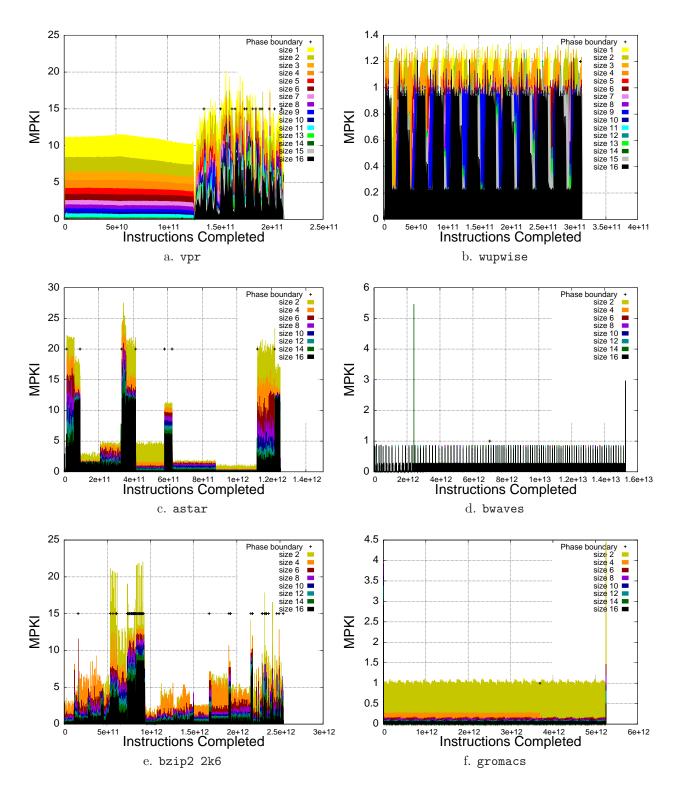

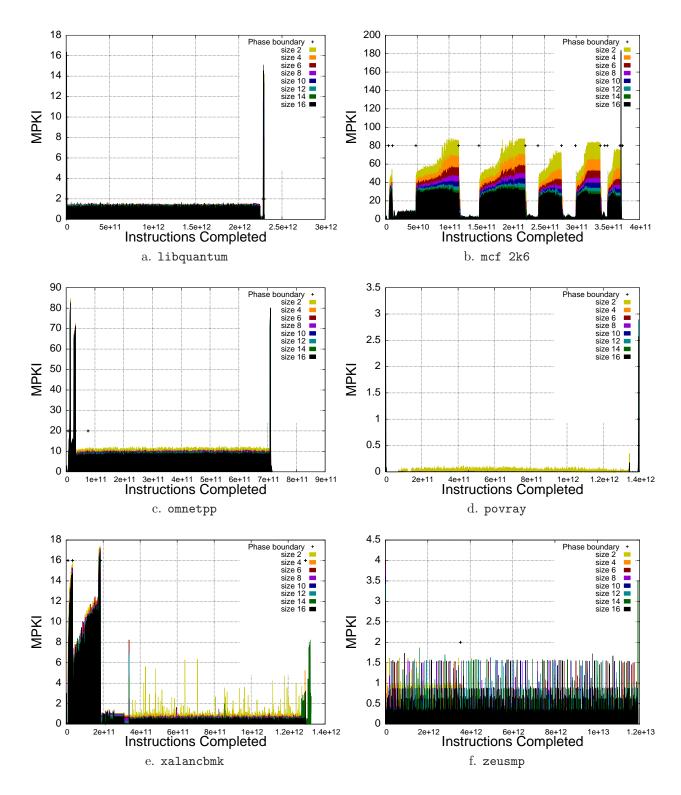

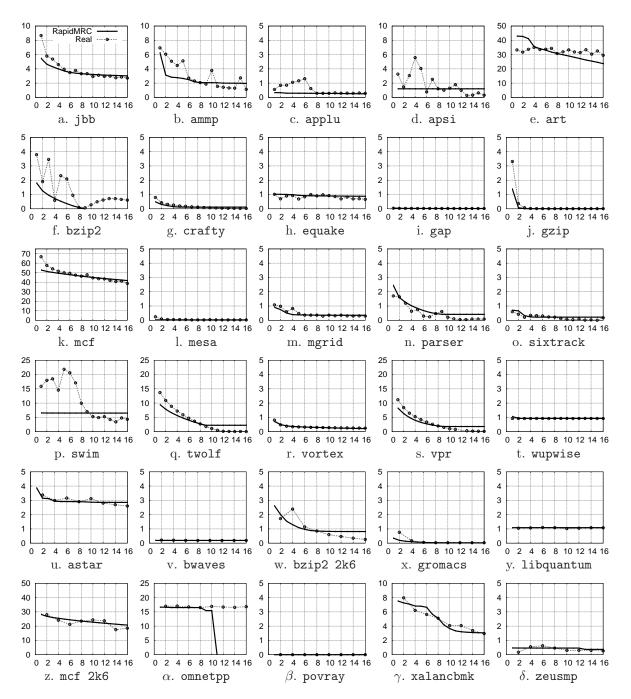

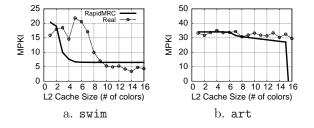

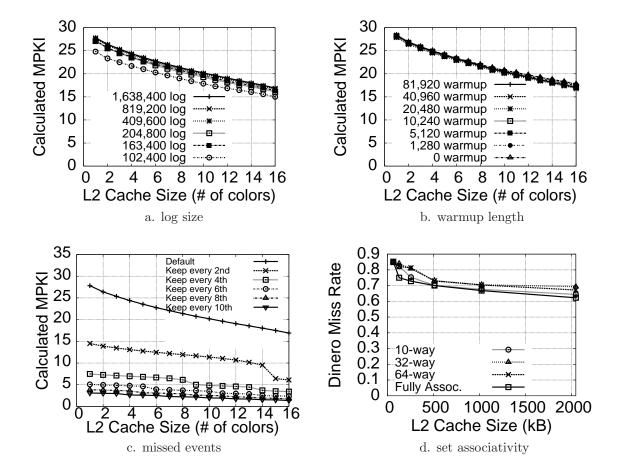

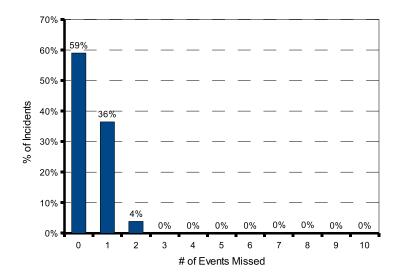

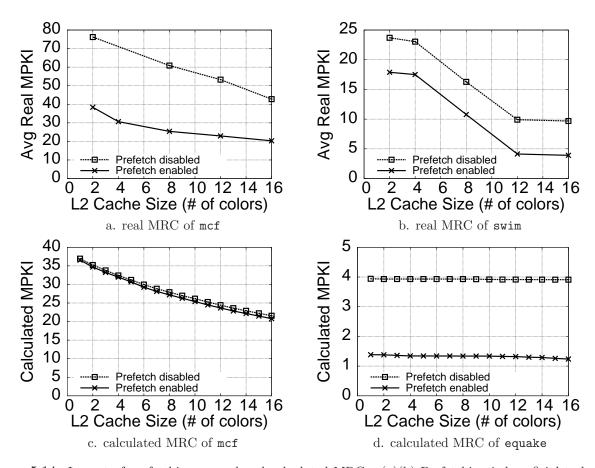

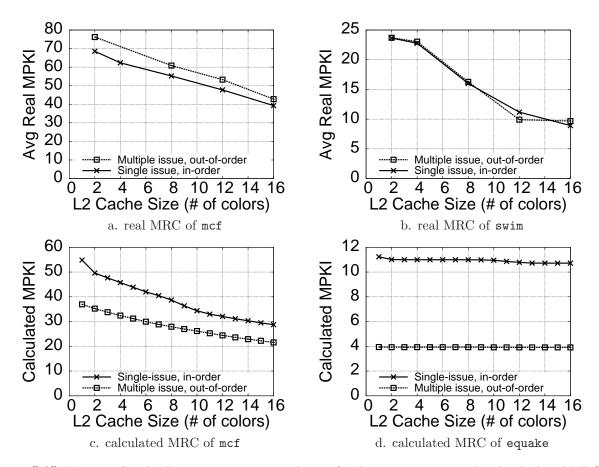

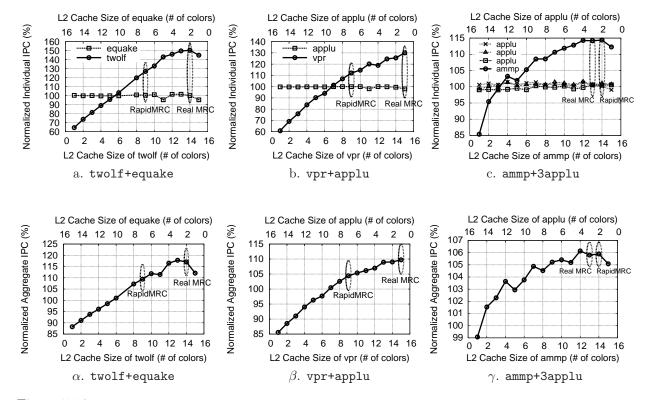

| Feb.  | 8-core IBM POWER7                  | L1,L2,L3       | L3     | [IBM 2010]              |  |  |  |  |